一直以来,人工智能AI的话题在学术界都比较热议,以前,人工智能技术并没有得到较快的发展,直至2006年,Hinton的“深度置信网络”概念使得该技术得到空前发展,接下来的人工神经网络不断被研究问世,各行各业人工智能也不断引进深度学习、人脸识别、自动化驾驶、图像分类识别等等都使用了先进的技术。

1. 卷积神经网络及异构计算理论基础

1.1 常见卷积介绍

(1)1x1卷积:其为二维卷积,并且是一个比较特殊的值,可以对卷积核数量进行调节,能够有效实现对特征图通道数的输出进行增减。

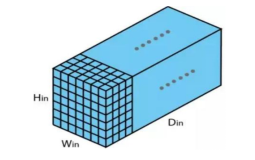

(2)3D卷积:一般2D卷积的滑动方向为宽-高,3D卷积的滑动方向还可以沿通道方向如图1所示。

图1 3D卷积

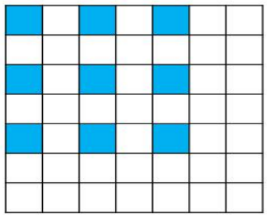

(3)空洞卷积:也被称之为膨胀卷积,其核内具有“空洞”,如果计算量不变,感受野扩大,空洞卷积将增加一个超参数,也就是膨胀率,卷积kernel内部的间隔如图2所示。

图2 空洞卷积

(4)深度可分离卷积:其组成主要分为深度卷积与逐点卷积,主要是为了使计算卷积量得以减少。如果输入特征图为宽高通道数-Wi*Hi*C,标准卷积大小为宽高通道数滤波器个数-Wc*Hc*C*N,输出特征图为Wo*Ho*N,得出标准卷积的计算量-Wo*Ho*N*Wc*Hc*C。在计算深度可分离卷积方面,通过采用Wc*Hc*1*C的深度卷积方法逐通道的方式进行计算,C作为卷积的组数,也就是标准卷积通道的数量,使用1*1*C*N卷积逐点进行计算,最终计算出其量值。

(5)可变形卷积:输入特征图中会有一部分非重要信息,由于其位置不同,将会有相应尺寸的形变物体,所以对图像特征进行提取时,应针对情况对感受野进行调整,但是由标准卷积大小的固定性的限制,感受野也会受到影响,在对图像特征进行提取时只能选取固定的位置。可变形卷积在此基础上增加相应的偏移量,可实现图像提取不同方面的偏移,提高了计算精度。

1.2 GPU硬件架构及其软件设计模型

由于GPU具有较强的可并行性,为当前阶段的深度学习模型训练与推理工作中做出较大贡献,卷积层等底层算子编写的通常是英伟达GPU中CUDA语言而实现,GPU与CPU相似的是其具有一定的内存,还被分为可编程与不可编程内存,其中可编程内存主要有:local memory-本地内存、register-寄存器内存、shared memory-共享内存、constant memory-常量内存、global memory-全局内存以及texture memory纹理内存等,不可编程内存为cache-缓存。GPU的访存速度与存储空间成反比。寄存器内存是可编程内存中访问速度最快的一种,寄存器内存具有很少的资源,寄存器内存中所存储数据可访问的仅为创建该存储器的线程。

补充寄存器内存的方式为本地内存,在寄存器内存满后本地内存就会发挥作用,其常会存储结构体或者数组较大的自动变量,事实上,全局内存与本地内存的存储区为同一个。使用__shared__来修饰共享内存变量,同一线程块中的线程会共同使用共享内存,其它线程块的共享内存不可以被一个线程块中的线程所访问,随着持续时间的推移,就其生命周期而言,可以将共享内存分为很多板块,实现同时访问。一般来说,GPU架构中,一个线程束是由32个线程而构成的,GPU中的warp是非常关键的存在,对已有的执行效率将产生重要的影响,如果在一个warp中线程不同的情况下对同一bank中不同字的地址进行访问时,就会出现bank冲突的情况,也就是访问方式成为串行访问,因此,在进行具体的编程操作中,这是一个值得关注的事项,防止出现降低程序执行效率的情况。纹理内部与常量内部都是只读内存中的组成部分,当同一内存地址在warp中的线程在进行读操作时,该数据的结束时间就会在16个线程结束,这样就可以实现少读15次。如果出现局部访问空间,可使用纹理内存,也就是在两个临近的线程读取位置十分接近时,纹理内存将快速实现读操作。由于GPU的全局内存特点在于较高的访问延时以及较大的空间,其变量包括动态与静态,cuda Malloc作为动态变量执行申请操作,__device__静态变量起到修饰作用。

2. GPU加速卷积层

2.1 GPU执行单元加速CNN的代价

GPU加速卷积层具有很多种计算方法,GEMM、Direct、Winograd以及FFT都可以实现,其中GEMM、Winograd以及FFT都属于矩阵的运算。所以硬件加速器的设计目的最终都是提升矩阵运算的速度。由于GPU的执行单元运行方式为SIMD,也就是一条指令可以进行多个计算。32个Data同时使用一个指令就是对其最好的诠释,而且,重点在于定义这32个Data的精度是单精度浮点数。为了实现对这些计算单元进行全面利用,从而将计算ALU的能力予以有效提升,半精度浮点的计算方式利用率也得到一定的认可。与单精度相对比,就性能方面而言,其将高于半精度浮点数2倍,因此,要对其以原基础进行支持,所用代价不需过高,最终通过GPU计算浮点的支持度与以CNN做推理相比较,其精度方面具有较大的提升。相关研究表明,8-bit整型数完全可以实现CNN推理,并且对最终的目标精度不会产生影响。对8-bit整型矩阵之间进行乘法运算而使用的逻辑门数目要与相同的浮点运算想对比而言,其可以具有较小的单元。

2.2 卷积神经网络加速算法

人工神经网络的构成内容就是连接几百万个神经元,在进行过深度学习反向训练后得出数以百万的权重以及偏斜值。“深度”二字所代表的是在网络中,由于连接神经元是分层的,下层神经元在输入上来源于上层神经元的输出。人工神经网络中有一种CNN-卷积神经网络,特点在于计算后得出的神经元能够作为图像卷积的集中,也就是在提取特征过程中是通过图像卷积来实现的,在对图像分类的时候就可以完全依靠于此,其可以广泛应用于图形处理器的芯片上。卷积层与矩阵加速单元最终能够实现矩阵运算的转化。并且比较普遍的算法就是GEMM。在计算输入特征图的卷积后,可以将其变为卷积核乘以一个展开的特征图矩阵,使用矩阵运算在对专用的矩阵加速单元实现加速方面更加便捷。

3.结语

文章主要介绍了GPU与数字图像处理算法,卷积神经网络中,计算卷积需要消耗较多内存,并且将会持续较长时间。所以通常使用矩阵乘法的方法实现卷积的计算,而在算法优化方面,通常会将矩阵乘法纳入研究领域内。文中通过GPU端对矩阵乘法进行优化,通过矩阵运算加速模块,将矩阵运算量予以大大降低,从而实现硬件性能的有效加速。

参考文献:

[1]何小庆.AIoT时代的嵌入式技术与人才培养[J].单片机与嵌入式系统应用,2020(09):06.

[2]筱原勇二.在嵌入式设备中实现AI性能的e-AI技术[J].电子产品世界,2017(12):21.

[3]Andrew Grant.为差异化AIoT应用提供GPU和神经网络加速器IP[J].电子产品世界,2020(04):19.

[4]张先轶.如何做嵌入式人工智能[J].软件和集成电路,2019(08):62-63.

[5]张平文.新图形,新AI解析Imagination新一代GPU及神经网络加速器[J].微型计算机,2019(01):89-92.

作者简介:卢孟(1985-12),男,汉族, 浙江慈溪市人,本科,主要从事公司项目决策管理。