随着航天技术的不断进步,SRAM型FPGA在航天器控制系统中的应用日益广泛。由于空间环境中存在大量高能辐射粒子,研究SRAM型FPGA的SEU故障注入技术对于提高航天器的安全性和可靠性具有重要意义。

1 故障注入系统设计

1.1 用户兴趣度的评分表示

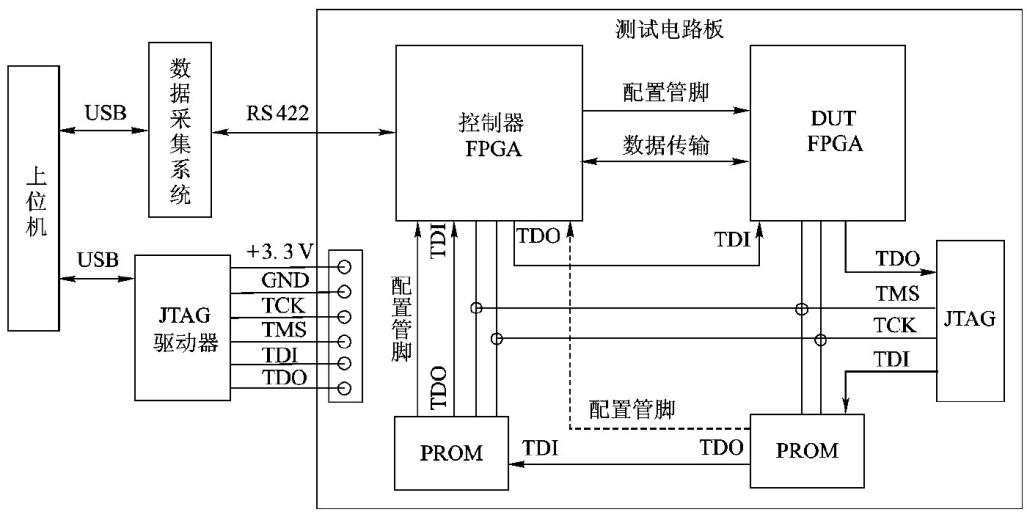

图1展示了故障注入系统硬件架构,由核心测试平台、数据传输链路及配套的计算机控制系统三大模块构成。其中,核心测试平台以主控现场可编程门阵列(FPGA)和被测FPGA及其固件存储器(PROM)为核心组件。主控FPGA执行关键职能,包括被测FPGA的初始化配置、数据读回、必要时的重新配置,以及对被测器件系统时钟频率的精确控制。数据传输链路作为通信桥梁,确保上位机准确向下向主控FPGA发送指令,同时高效回传主控FPGA从被测FPGA获取的实时反馈数据至上位机。

图1 故障注入系统框图

图1 故障注入系统框图

1.2 主控FPGA软件设计

主控FPGA的逻辑架构主要包含六个功能区块以及两种关键数据存储元件。首先,为被测FPGA的初始化设置模块,其次为与上级控制器通信的接口模块,其负责接收上位机各类指令。当接收到指令后,系统流程进入命令解析判断阶段,根据指令类型确定响应方式。具体而言,若判断为重配置指令,系统将依据预载的重配置命令字及相关数据存储模块,启动重配置子系统对被测FPGA进行重新编程。反之,若识别为读取状态指令,则由回读控制模块运用存储的回读命令字激发被测FPGA的数据反馈功能,通过通信链路将回读信息返回上位机进行后续处理。

2 故障注入试验及结果分析

2.1 测试对象

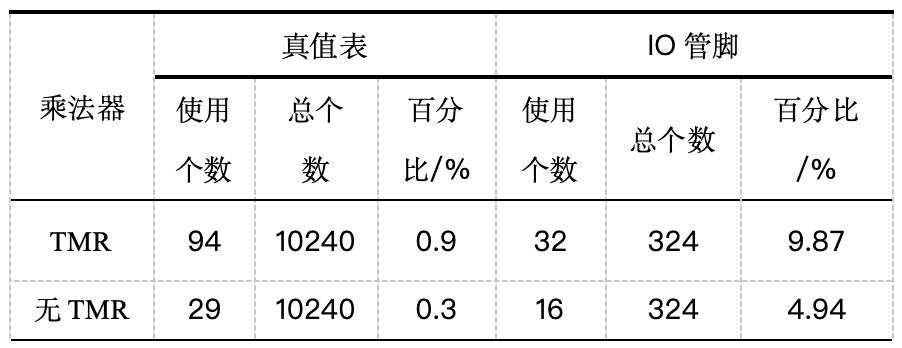

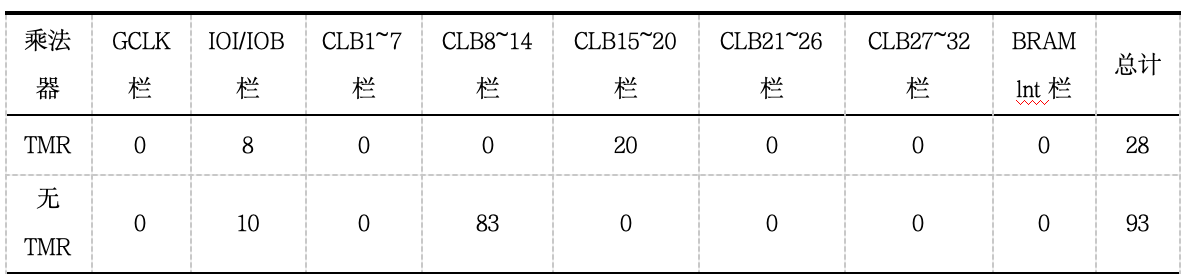

针对具备TMR设计与无TMR设计的乘法器,分别实施了翻转故障实验,并对所得测试结果进行了对比分析。

TMR采用输入和乘法模块均三模冗余,采用单表决器输出的设计方法。同时,为了避免TMR单点失效问题,各模块进行了布局操作。将M1模块放置于CLB(Control Logic Block)1~7栏,M2放置于CLB8~14栏,M3放置于CLB21~26栏,V0放置于CLB15~20栏。将所有的输入输出放置在芯片左侧和右侧的管脚。未经过TMR设计的乘法器其乘法器模块放置于CLB8~14栏。乘法器输入为4位×4位,输出为8位。两种设计的资源使用情况如表1所示。

表1 两种设计资源使用情况

2.2 测试结果

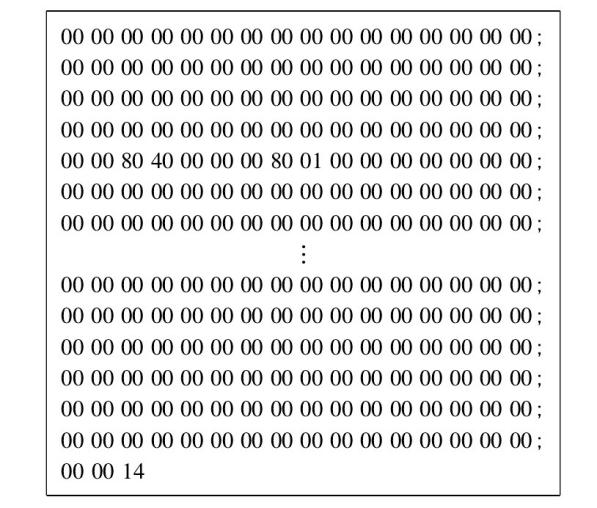

对上述设计进行试验,结果如表2所示。TMR乘法器CLB15~20栏翻转试验生成的msk.dat文件截取部分如图2所示。文件中为1的位即表示配置数据中相应位为敏感位,最后3个字节代表敏感位的总位数。对msk文件进行简单分析即可得敏感位的具体位置,见表3。

表2 翻转试验结果

图2 TMR乘法器CLB15~20栏msk.dat文件

图2 TMR乘法器CLB15~20栏msk.dat文件

表3 TMR乘法器CLB15~20栏敏感位位置

2.3 结果分析

根据试验结果可以得到如下分析:

1) 当前设计方案构建为纯组合逻辑架构,并未引入时钟元件及BRAM资源,故而,所有关键变量皆严格限于CLB区块及其关联的IOI/IOB组件之中。

2) 在实施三模冗余(TMR)策略的CLB区域内,敏感性依赖仅存在于表决模块内部,强化表决模块自身的稳健性或是采取多重表决机制将是合理路径,这一结论与理论预测相互印证。

3) 针对时序逻辑电路进行故障注入测试时,预先确定故障传播至输出端所需的最大时序周期至关重要,以便在判定故障时适配相应的延时处理。

4) 在发生状态反转的配置存储位中,部分包含了用户定义的存储单元,这些单元直接影响触发器的功能特性;尽管如此,触发器占用的整体资源量极微,大致占据0.42%的空间,因而在评估全局效能时可视为次要因素。

5) 该方法目前限定于单一位翻转的模拟场景,对于涵盖两位及以上同步翻转的全面扫描并非可行之举。然而,实际上,由单粒子效应引发的绝大多数(超过95%)事件为单位翻转,故此限制并不妨碍利用本方法对系统可靠性的实质性评估。

对

4 总结

采用的反转错误注入技术手段,旨在揭示用户定制电路设计中配置存储单元的敏感比特位置,并描绘出电路在太空环境下的可靠性演变曲线,有效评估其在实际应用场景下的性能稳定程度。此测试过程高效快捷,整个实验周期被控制在仅仅33分钟之内;实验成果不仅囊括了敏感比特数量的统计,更实现了对这些关键位置的精确定位。下一步,对于多比特并发反转、累积翻转错误以及单粒子触发的功能中断故障场景下的故障注入策略尚有待深入探究与发展。

参考文献

[1] 严健生,杨柳青. 卫星用SRAM型FPGA抗单粒子翻转可靠性设计研究[J]. 科技创新与应用,2021(9):48-50,53.

[2] 陈冬梅,谭志新,孙旭朋,等. SRAM型FPGA散裂中子源反角白光中子单粒子试验[J]. 航空科学技术,2021,32(2):62-65.

[3] 王梦茹,周珊,张弛,等. 一种SRAM型FPGA单粒子故障注入实验集的筛选方法[J]. 微电子学与计算机,2021,38(1):38-44.

[4] 王梦茹. 空间环境下SRAM型FPGA单粒子故障注入关键技术研究[D]. 中国科学院大学,2021.